# 第2章 组成篇

# 1. 计算机的总线

# 1.1 作用

- 解决不同设备之间的通信问题。

USB(Universal Serial Bus):

- 提供了对外连接的接口

- 不同设备可以通过 USB 接口进行连接

- 连接的标准,促使外围设备接口的统一

# 1.2 分类

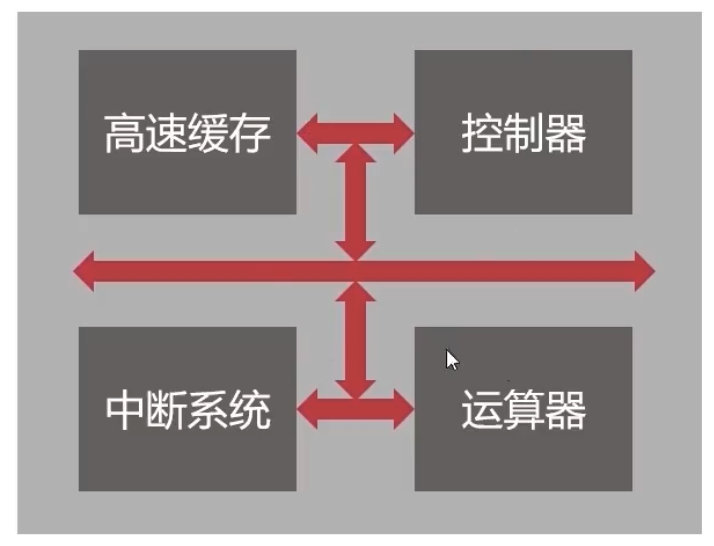

片内总线:高集成度芯片内部的信息传输线

芯片内部的总线

寄存器与寄存器之间

寄存器与控制器、运算器之间

系统总线:连接计算机外围设备的总线

- 数据总线

- 地址总线

- 控制总线

# 1.2.1 数据总线

- 双向传输各个部件的数据信息

- 数据总线的位数(总线宽度)是数据总线的重要参数,一般与 CPU 位数相同(32位、64位)

# 1.2.2 地址总线

- 用于数据的寻址

- 地址总线位数 = n,寻址范围:0-2^n^

- 地址总线的位数与存储单元有关

# 1.2.3 控制总线

- 用来发出各种控制信号的传输线

- 控制信号由控制总线从一个组件发送到另外一个组件

- 控制总线可以监视不同组件之间的状态

# 1.3 仲裁

仲裁器用来解决总线使用权的冲突问题。

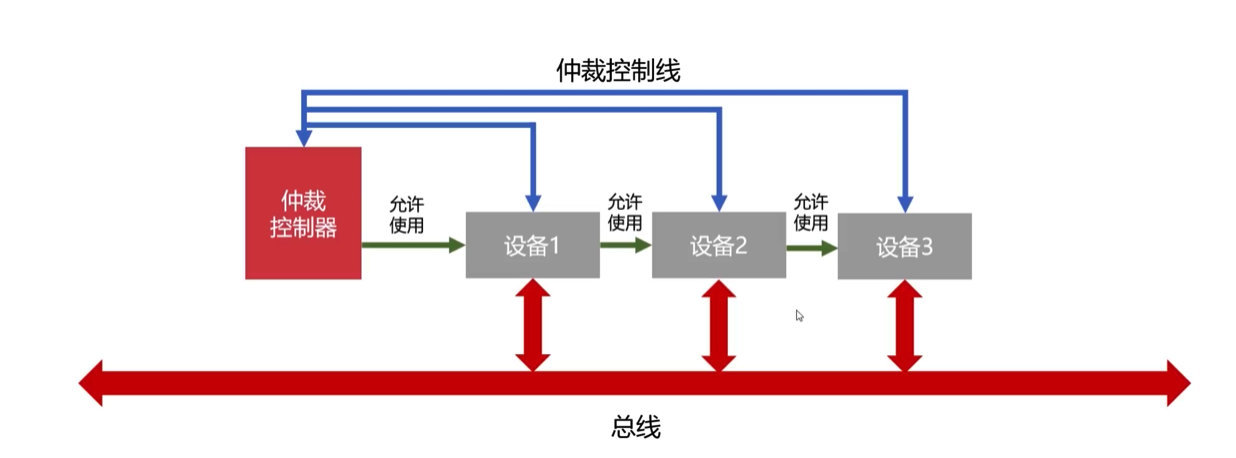

# 链式查询

如果设备 2 发出使用总线的请求,那么就会经由仲裁控制线到达仲裁控制器,仲裁控制器接收到这个请求后就会发出允许使用的指令。但是该指令会先到达设备 1,如果设备 1 不需要使用总线的话,就会传到设备 2。设备 2 拿到这个指令后就可以使用总线了。

- 电路复杂度第,仲裁方式简单

- 优先级低的设备难以获得总线使用权

# 计时器定时查询

- 仲裁控制器对设备编号并使用计数器累计计数

- 仲裁控制器接收到仲裁信号后,往所有设备发出计数值

- 计数值与设备编号一致则获得总线使用权

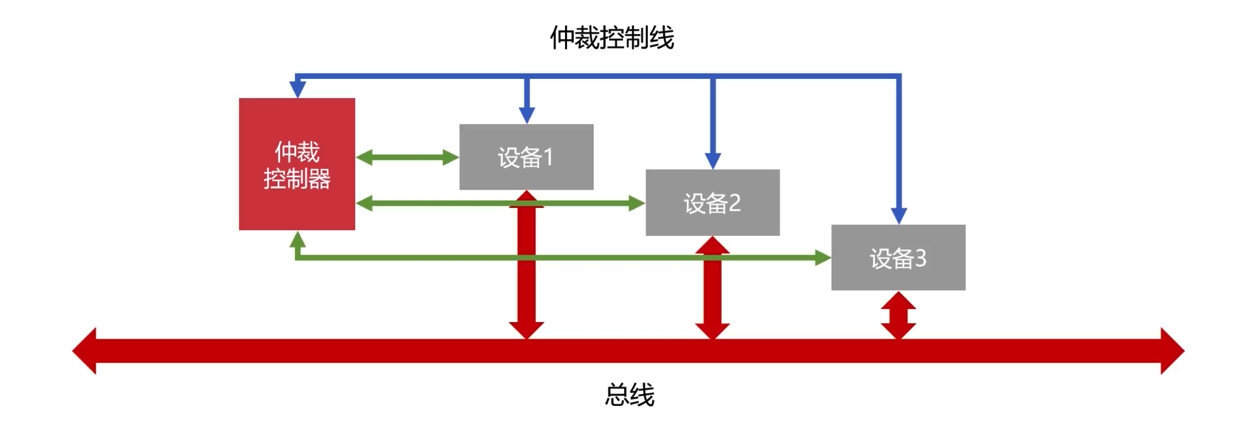

# 独立请求

- 每个设备均有总线独立连接仲裁器

- 设备可单独向仲裁器发送请求和接收请求

- 当同时收到多个请求信号,仲裁器有权按优先级分配使用权

- 响应速度快,优先顺序可动态改变

- 设备连接多,总线控制复杂

# 2. IO 设备

# 2.1 输入输出接口的通用设计

- 如何读取数据?

- 如何向设备发送数据?

- 设备有没有被占用?

- 设备是否已经连接?

- 设备是否已经启动?

# 2.1.1 数据线

- 是 IO 设备与主机之前进行数据交换的传送线

- 单向或双向

# 2.1.2 状态线

- IO 设备状态向主机报告的信号量

# 2.1.3 命令线

- CPU 向设备发送命令的信号线

- 发送读写信号

- 发送启动停止信号

# 2.1.4 设备选择线

- 主机选择与 IO 设备进行操作的信号线

# 2.2 CPU 与 IO 设备的通信

# 2.2.1 程序中断

- 当外围 IO 设备就绪时,向 CPU 发送中断信号

- CPU 有专门的电路响应中断信号

- 程序中断提供低速设备通知 CPU 的一种异步方法

- CPU 可以高速运转同时兼顾低速设备的响应

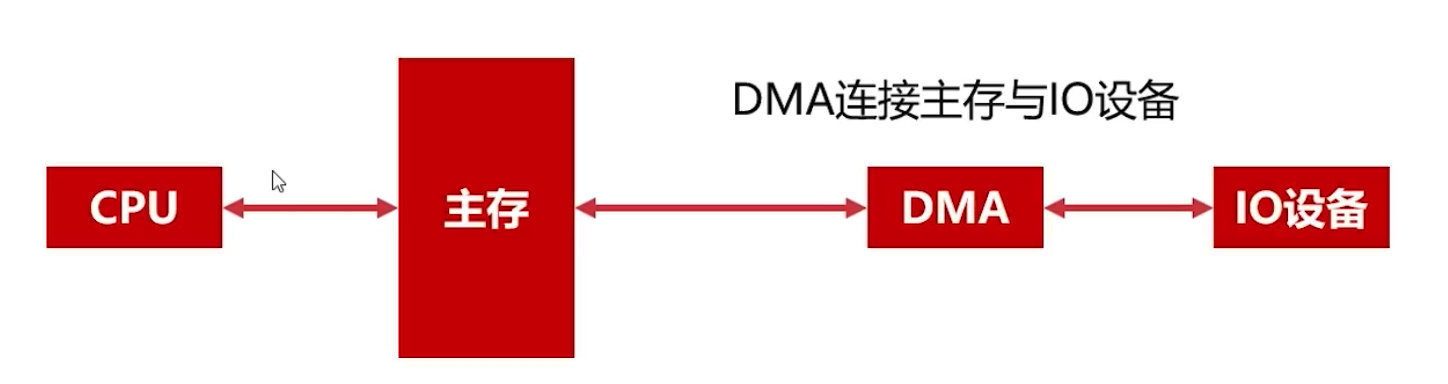

# 2.2.2 DMA(直接存储器访问)

- DMA 直接连接主存与 IO 设备

- DMA 工作时不需要 CPU 的参与

- DMA 可以提高 CPU 效率

# 3. 存储器

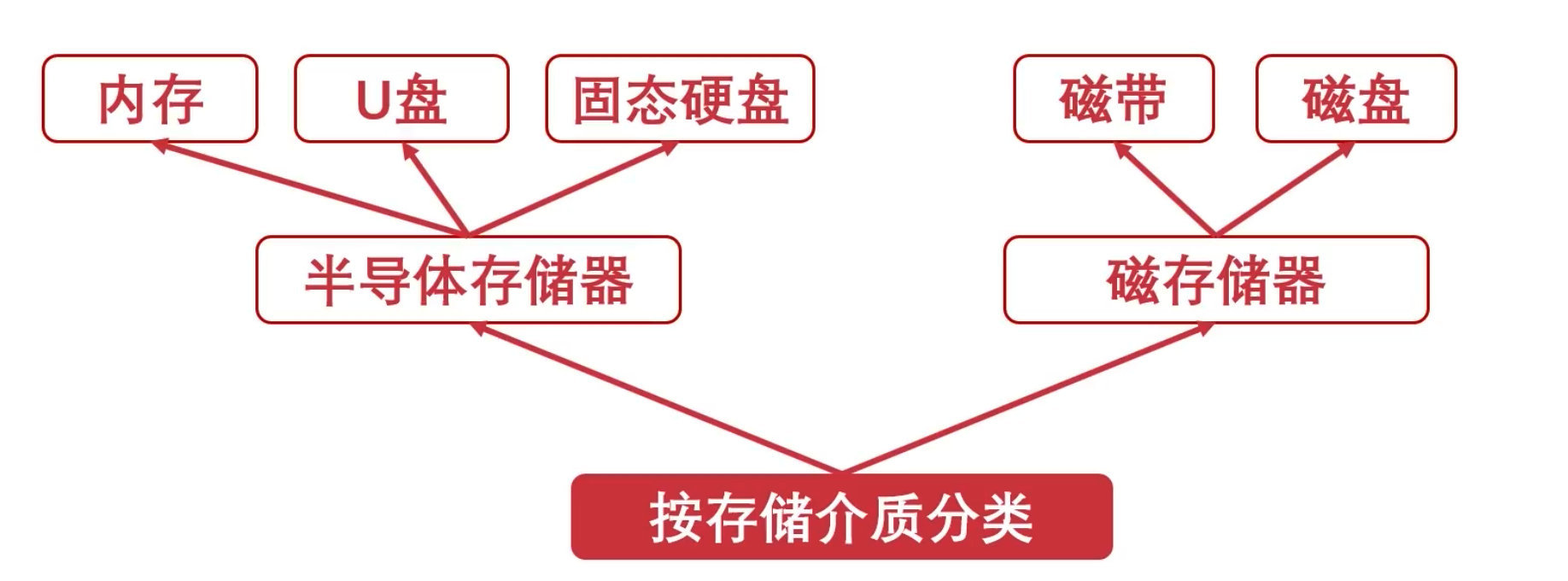

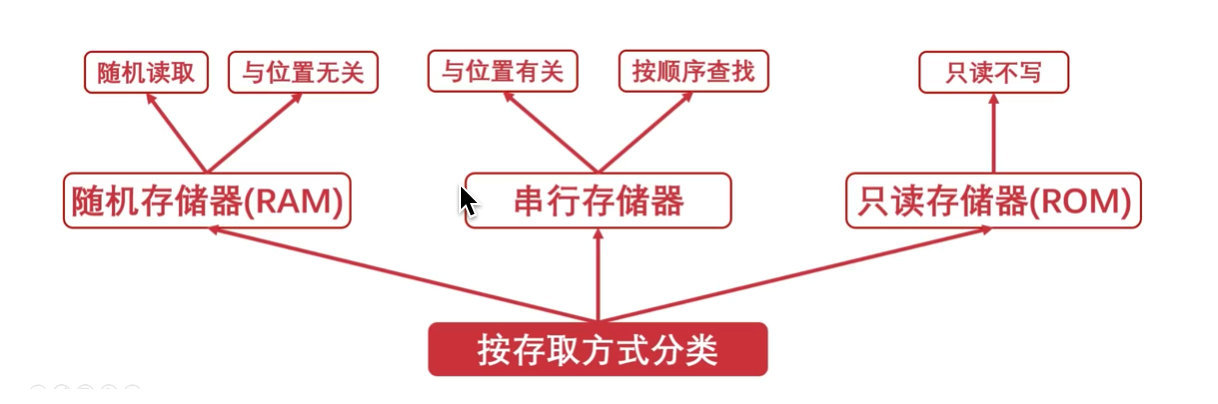

# 3.1 分类

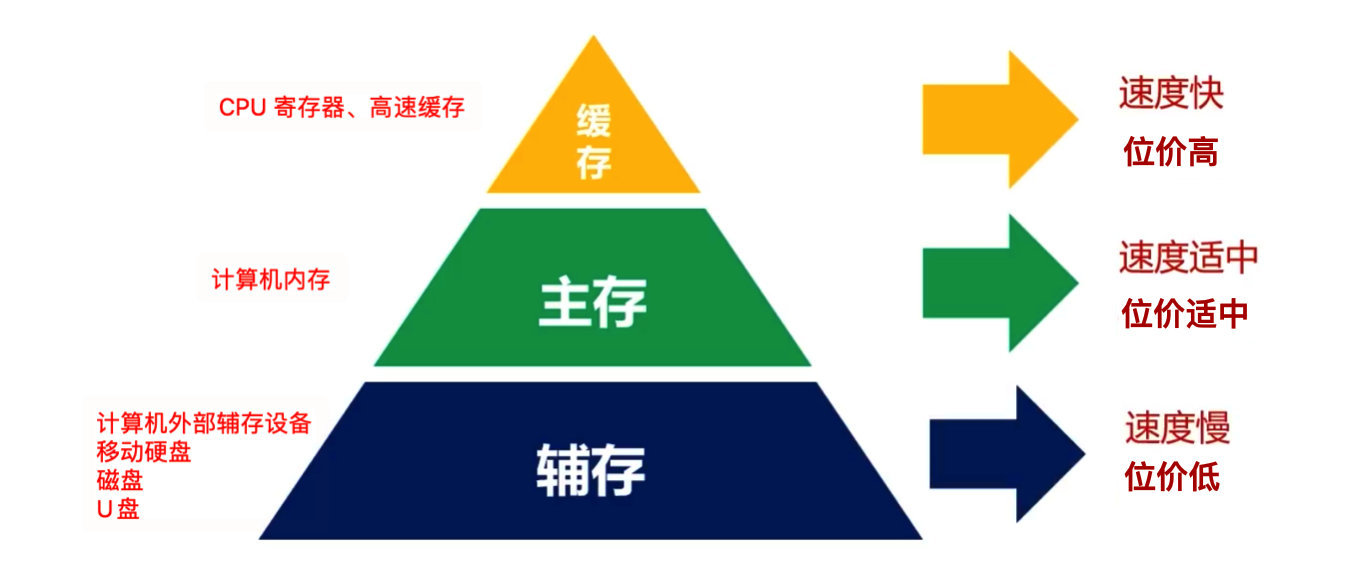

# 3.2 层次结构

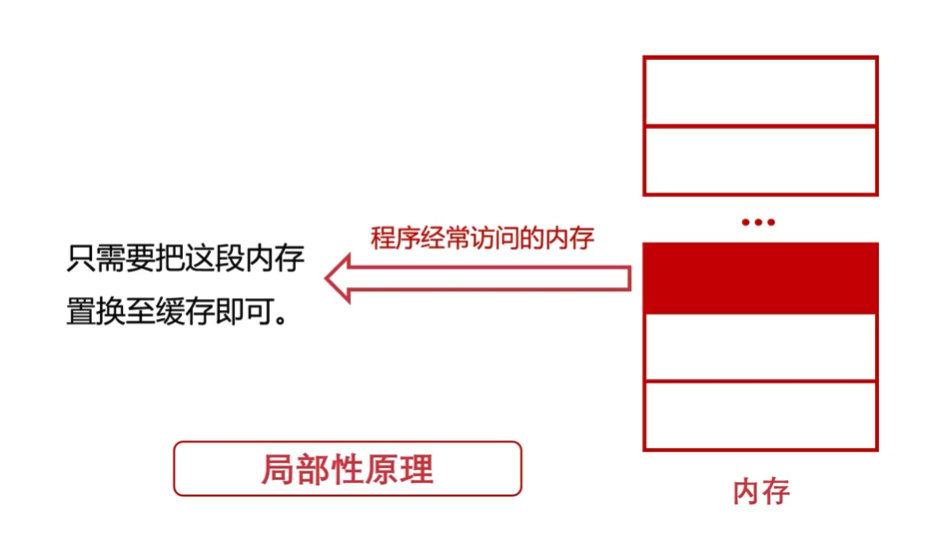

# 3.2.1 缓存-主存层次

原理:

- 局部性原理

# 局部性原理

局部性原理是指 CPU 访问存储器时,无论是存取指令还是存取数据,所访问的存储单元都趋于聚集在一个较小的连续区域中。

# 3.2.2 主存-辅存层次

原理:

- 局部性原理

实现:

- 主存之外增加辅存存储器(磁盘、SD卡、U盘等)

目的:

- 解决主存容量不足的问题

# 3.3 主存储器/辅助存储器

# 主存储器 —— 内存

- RAM(随机存取存储器:Random Access Memory)。

- RAM 通过电容存储数据,必须隔一段时间刷新一次。如果断电,那么一段时间后将丢失所有数据。

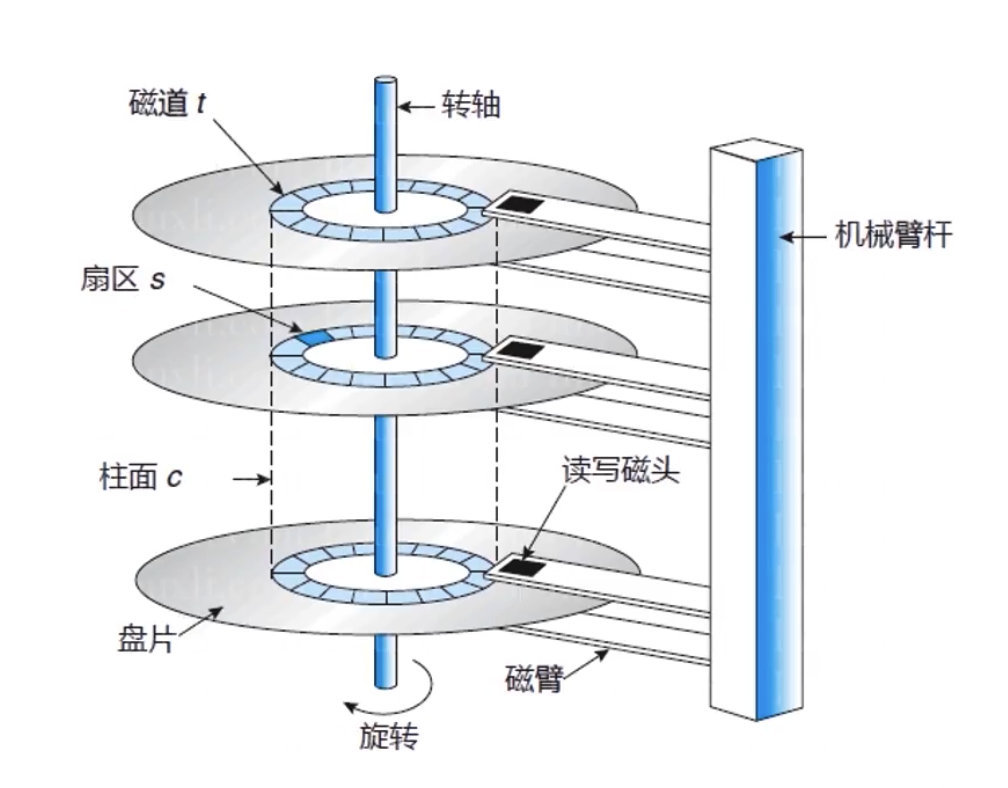

# 辅助存储器 —— 磁盘

- 表明是可磁化的硬磁特性材料。

- 移动磁头径向运动读取磁道信息。

调度算法:

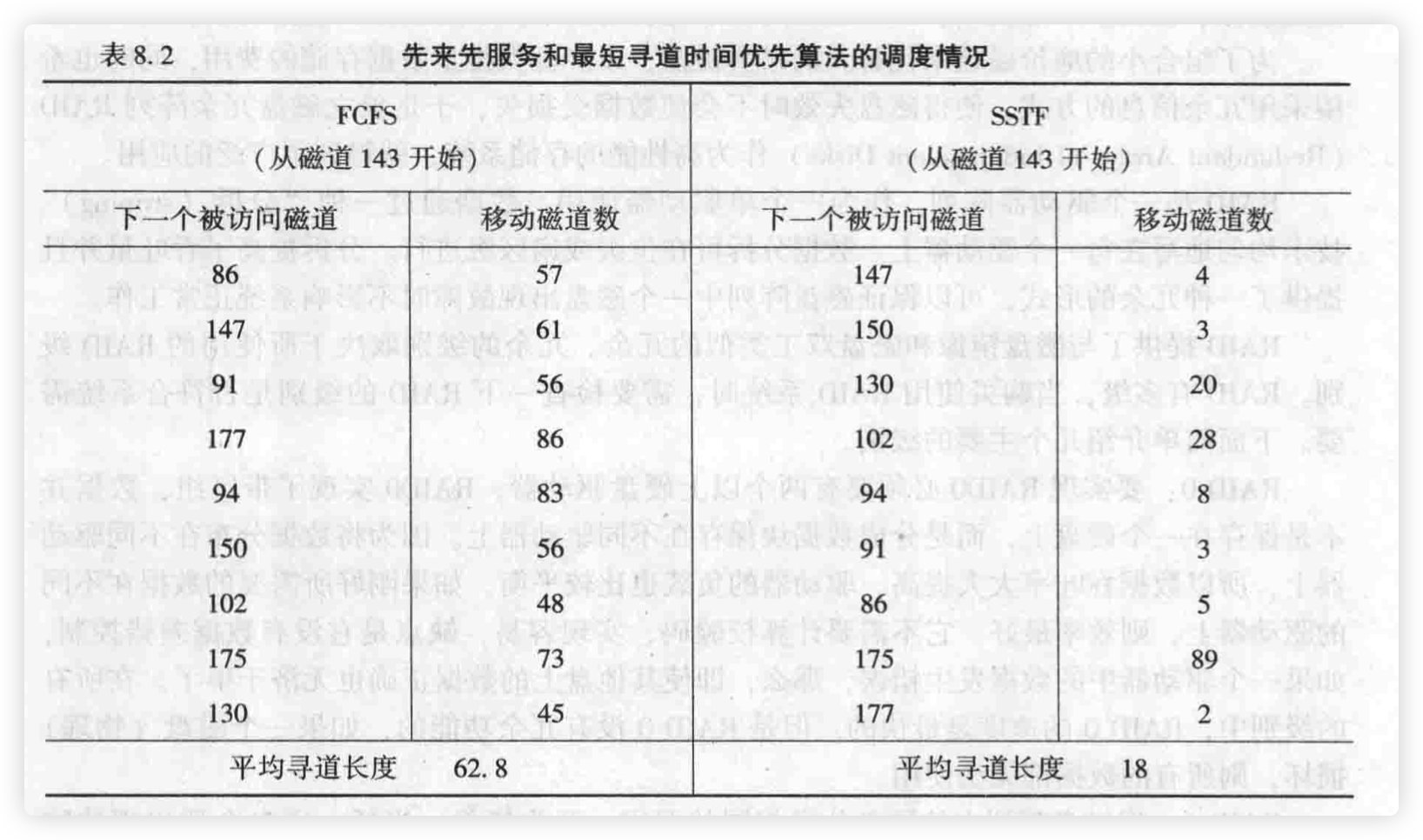

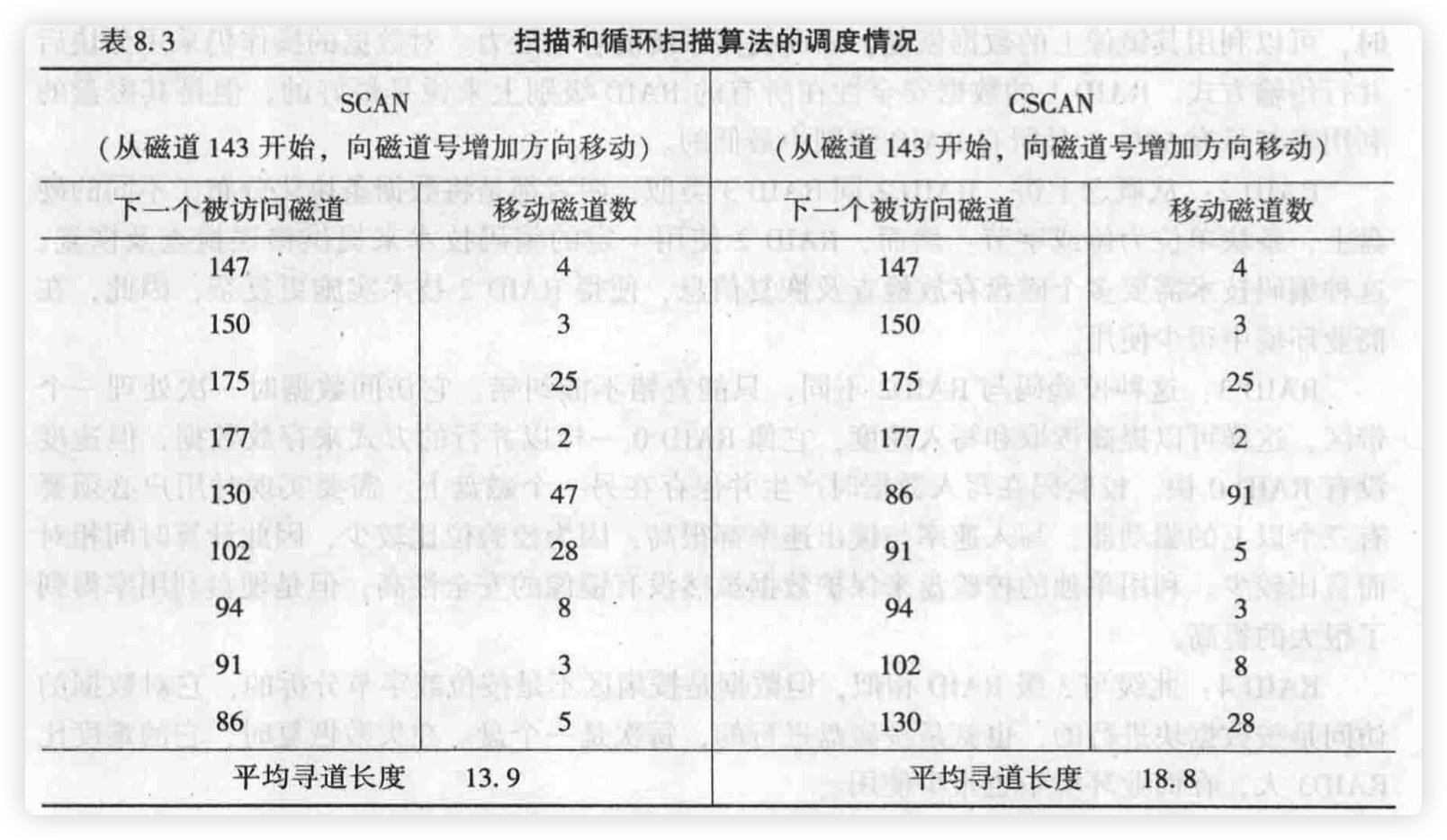

例如,有一个磁盘请求序列,其磁道号为: 86、147、 91、177、94、150、 102、175、130,磁头当前正在143号磁道上并向磁道号增加的方向移动。

- 先来先服务算法

- 最短寻道时间优先

- 扫描算法(电梯算法)

- 在磁头当前移动方向上选择与当前磁头所在磁道距离最近的请求作为下一次服务的对象。因这种算法中磁头移动规律颇似电梯的运行,故又称为电梯调度算法。

- 特点:具有较好的寻道性能,能避免进程饥饿,但不利于两端磁道的请求。

- 循环扫描算法

- 是SCAN算法的改良,它规定磁头==单向移动==。例如,自里向外移动,当磁头移到最外磁道时==立即又返回到最里==磁道,如此循环进行扫描。

- 特点:该算法消除了对两端磁道请求的不公平。

# 4. 高速缓存

# 4.1 重要概念

# 字

是指存放在一个存储单元中的二进制代码组成。

# 字块

存储在连续的存储单元中而被看作一个单元的一组字。

# 字的地址

- ① 前 m 位指定字块的地址

- ② 后 b 位指定字在字块中的地址

# 假设主存用户空间容量为 4G,字块大小为 4M,字长为 32 位,则对于字地址中的块地址 m 和块内地址 b 的位数,至少应该是多少?

4G = 4096M

故字块数 = 4096M/4M = 1024

故块地址位数 m = 10

由于字节快大小为 4M,字长为 32 位

故一个字块拥有的字数为 = 4M / 32bit = 4*1024*1024*8/32 = 2^20^

故块内地址位数 b = 20

# 4.2 工作原理

- CPU 需要的数据在缓存里就直接从缓存中拿

- 如果缓存中没有,那就去主存拿

# 4.3 替换策略

- 随机算法

- 先进先出算法 FIFO

- 最不经常使用算法 LFU

- 最近最少使用算法 LRU

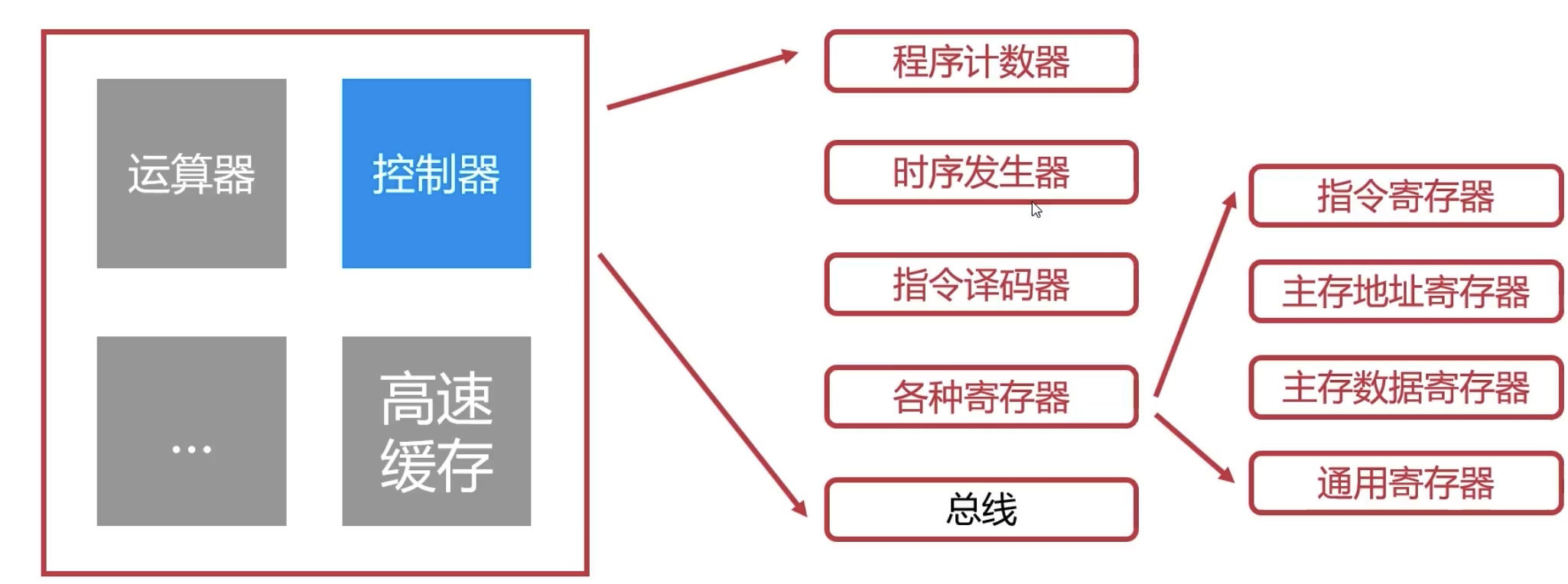

# 5. 控制器

协调和控制计算机运行。

# 程序计数器

- CPU 用来存储下一条指令的地址;

- 循环从程序计数器中拿出指令,当指令被拿出时,指向下一条指令。

# 时序发生器

- 电气工程领域,用于发送时序脉冲;

- CPU 依据不同的时序脉冲有节奏的进行工作。

# 指令译码器

- 计算机指令由操作码和地址码组成;

- 翻译操作码对应的操作以及控制传输地址码对应的数据。

# 指令寄存器

- 从主存或高速缓存取出计算机指令,是使得 CPU 可以高速运转的一个重要部件之一。

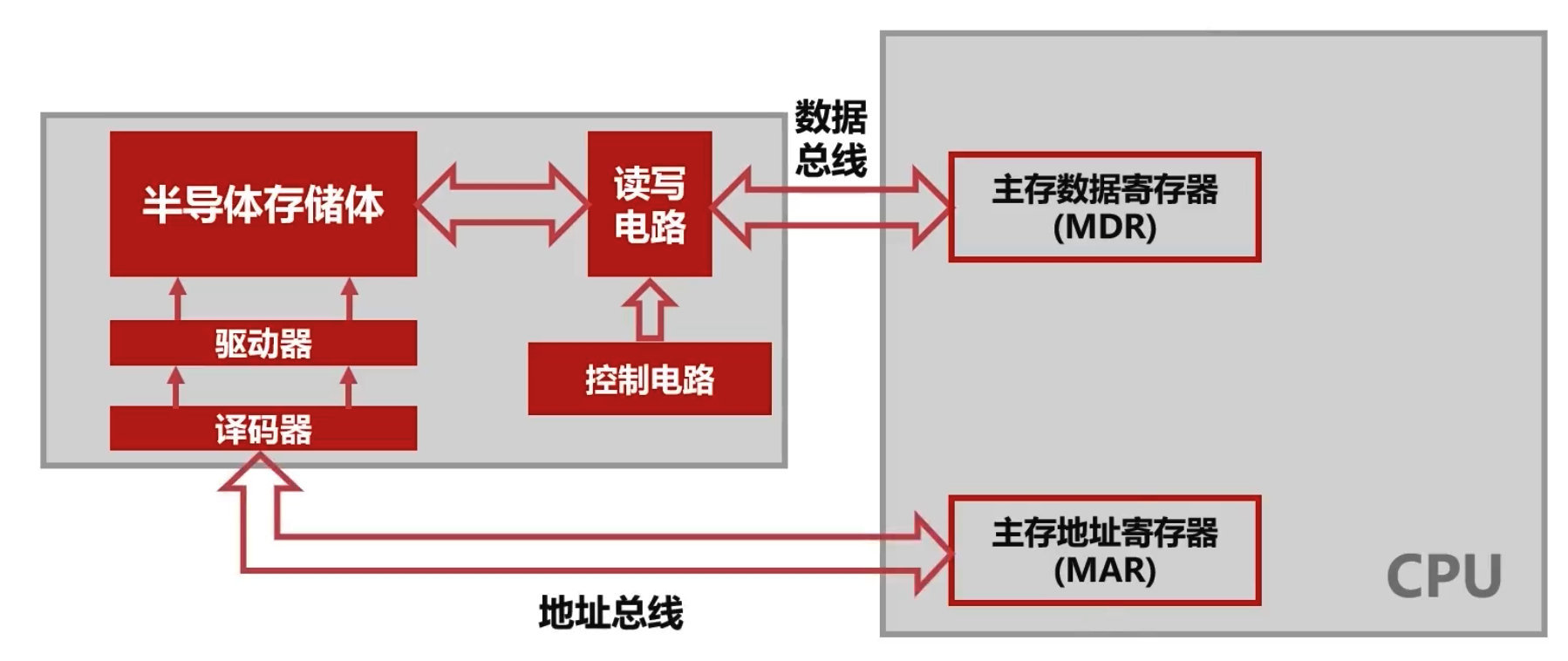

# 主存地址寄存器

- 保存当前 CPU 正要访问的内存单元的地址。

# 主存数据寄存器

- 保存当前 COU 正要读或者写的主存数据。

# 通用寄存器

- 用户暂时存放或传送数据或指令;

- 可保存 ALU 的运算中间结果;

- 容量一般比专用寄存器要大。

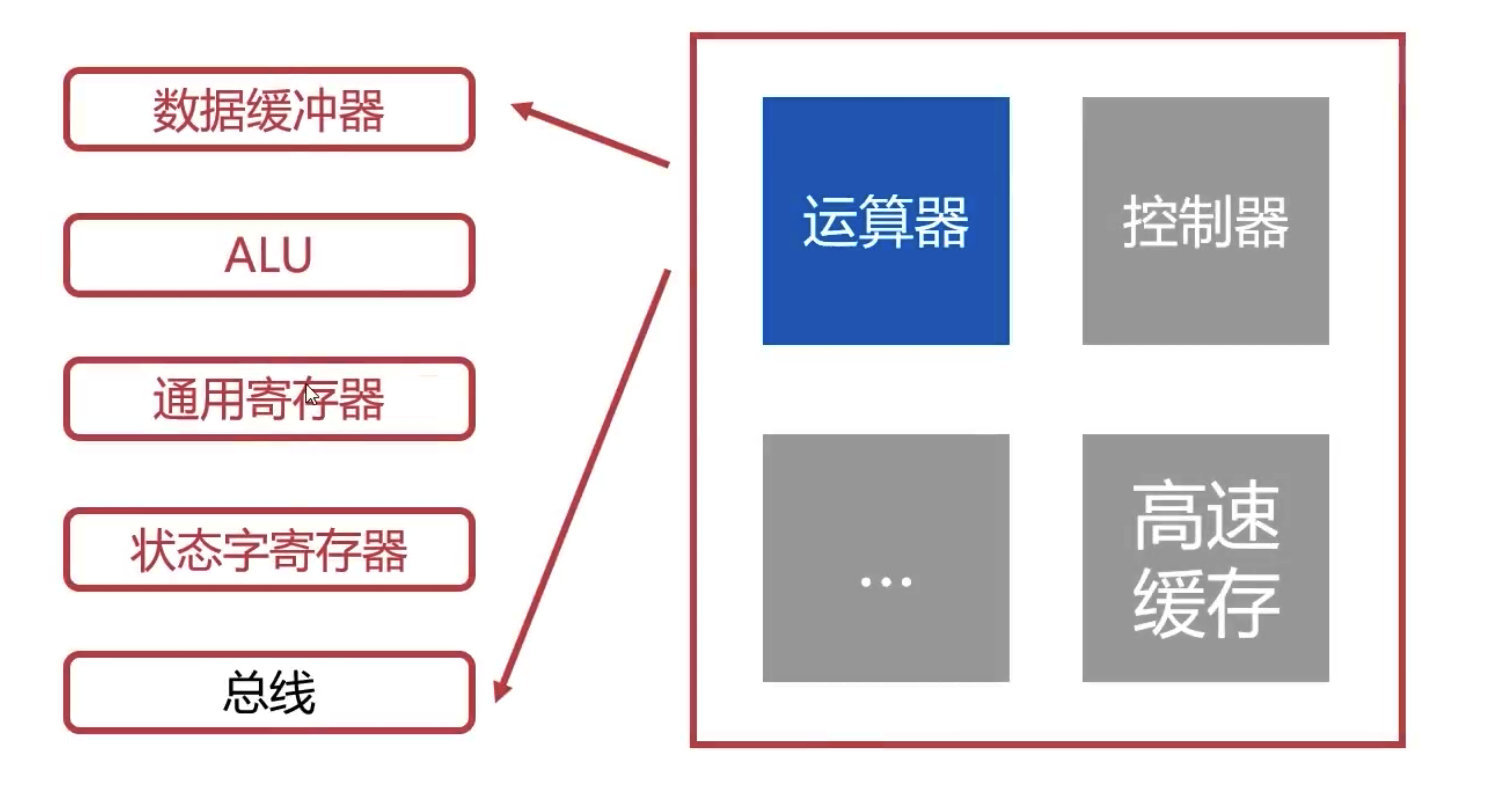

# 6. 运算器

进行数据运算加工。

# 数据缓冲器

- 分为输入缓冲和输出缓冲;

- 输入缓冲暂时存放外部设备送过来的数据;

- 输出缓冲暂时存放往外部设备的数据。

# ALU(Arithmetic logic unit,算术逻辑单元)

- 常见的位运算(左右移,与或非)

- 常见的算数运算

# 通用寄存器

- 用于暂时存放或传送数据或指令;

- 可保存 ALU 的运算中间结果;

- 容量一般比专用寄存器要大。

# 状态字寄存器

- 存放运算状态(条件码、进位、溢出、结果正负等);

- 存放运算控制信息(调试跟踪标记位、允许中断位等)。

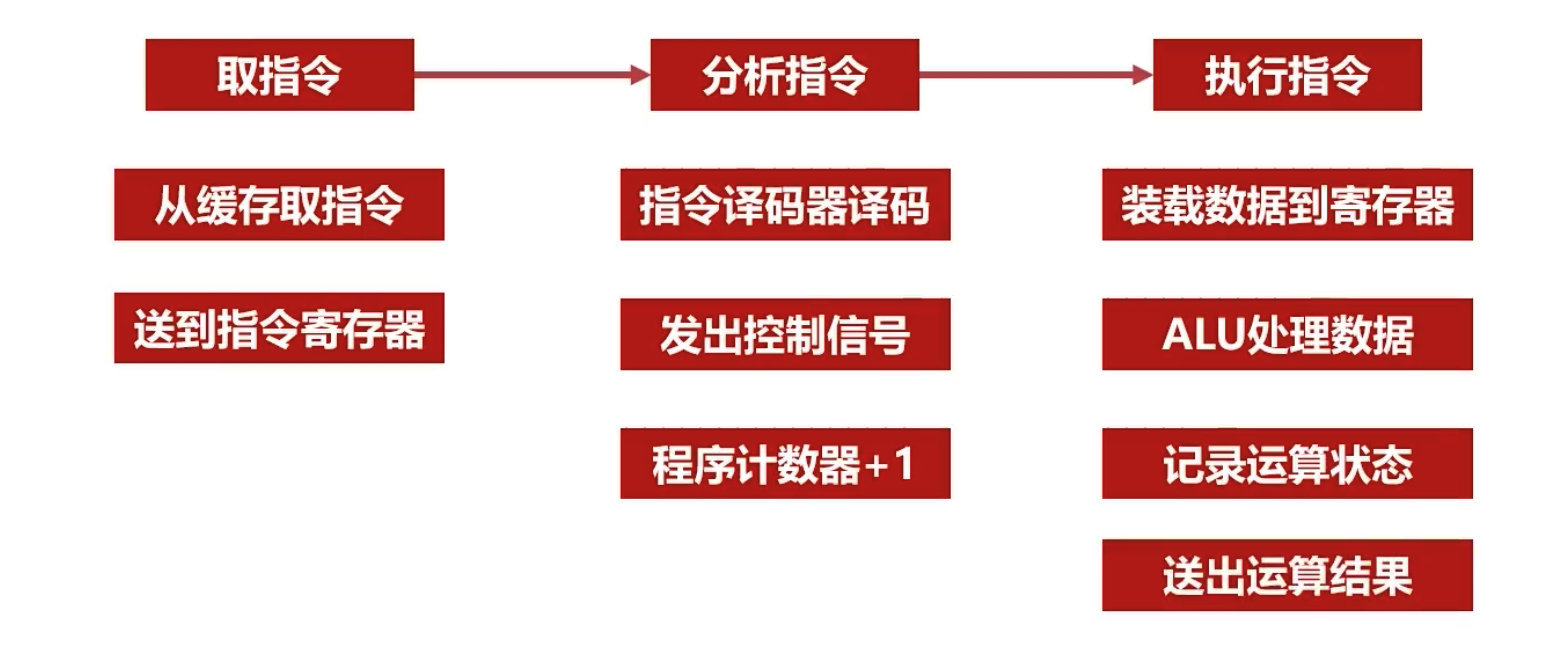

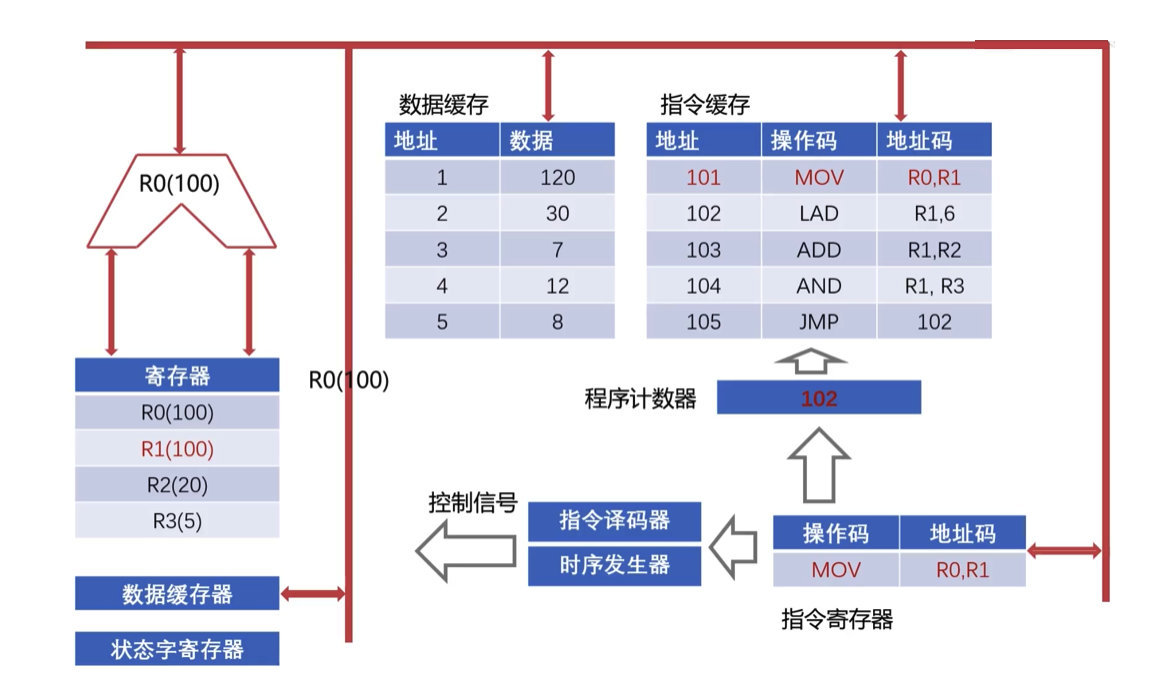

# 7. 计算机指令的执行过程

← 第1章 概述篇